Analog Front-End Electronics

F E E

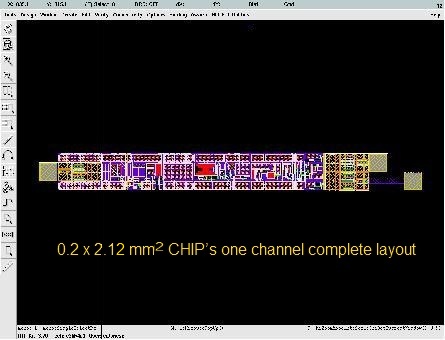

| • | the chip is developed in AMS CMOS 0.35 mm technology |

| • | acts as an analog, self triggered front end signal processor for HCR-TRD |

Goals:

| • | for testing the new HCR TRDs |

| • | for evaluating different solutions for the HCR TRD front end electronics |

Specifications:

| ■ | Number of analog channel: 8 |

| ■ | Analog channel outputs: a) fast semi-Gaussian output signal b) peak-sense output signal |

| ■ | In chip pulse generator for testing analog channels |

| ■ | Channel self triggered capability |

| ■ | Input/Output interface on request/grant basis |

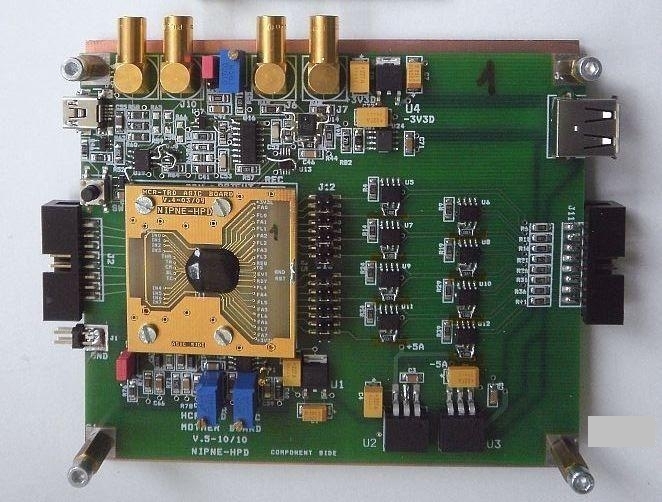

ASIC test needs an appropriate infrastructure.

It was designed, built and tested:

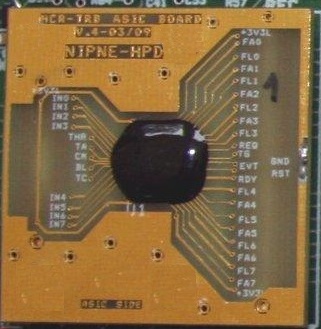

- PCB - as chip mounting/bonding base

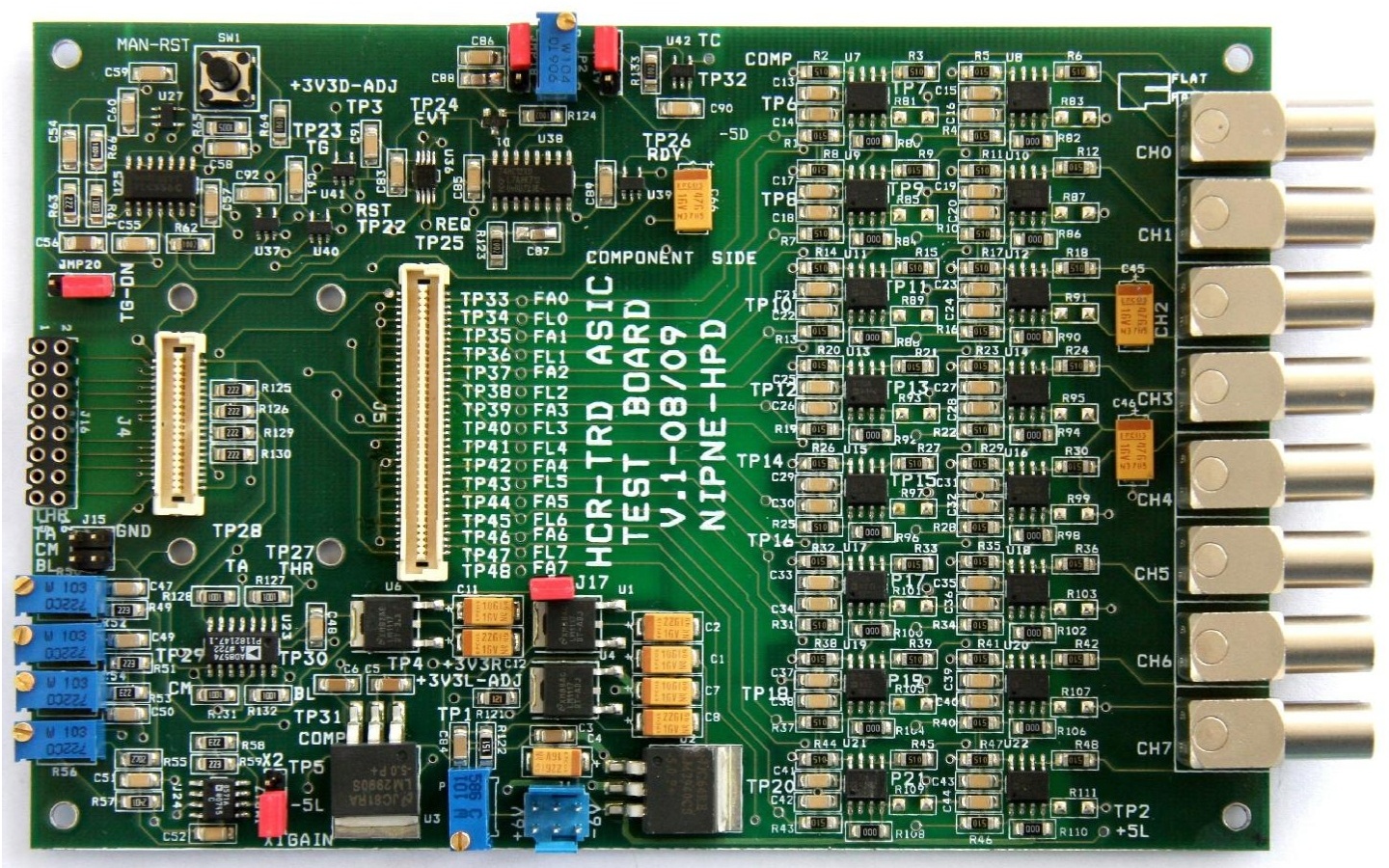

- Test Board - for electronic tests of the chip

- Mother Board - for testing the chip as HCR-TRD FEE

It was designed, built and tested:

- PCB - as chip mounting/bonding base

- Test Board - for electronic tests of the chip

- Mother Board - for testing the chip as HCR-TRD FEE